解构PLP翘曲难题:低温固化PSPI与Balance Film技术解析与供应商格局

摘要

2026年台积电预计透过子公司采钰建置CoPoS实验产线,并预计在2027年试产,因此2026年为相关设备、材料商的验证、出货关键时间点。为解决大面积面板级封装(Panel-Level Packaging,PLP)伴随的翘曲问题,山太士、晶化科、永光等特化厂商纷纷于Touch Taiwan 2026论坛上提出相应的解决方案,成为市场关注的焦点。

因此本篇报告主要深度解析:(1) PLP的背景与展望;(2)翘曲成因与解决方案;(3)抑制翘曲的材料与相关供应商。期能解析PLP需求动能、panel翘曲原理与可能之解决方案,以及台湾厂商的潜在商机。

一. PLP的背景与展望

二. 翘曲成因与解决方案

三. 抑制翘曲的材料与相关供应商

四. 拓墣观点

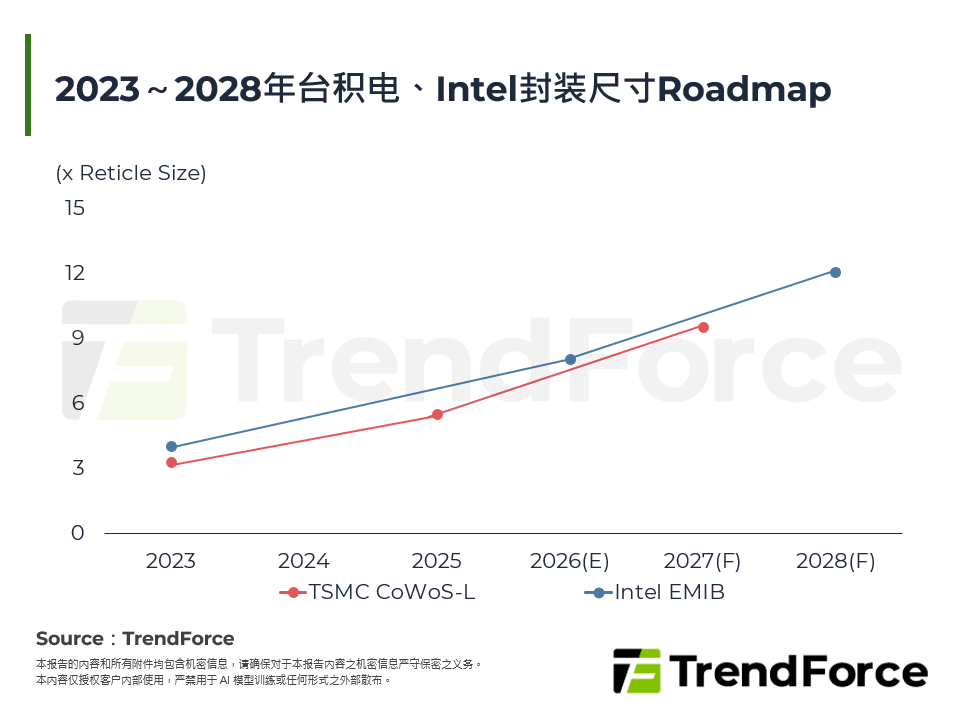

图一 2023~2028年台积电、Intel封装尺寸Roadmap

图二 各尺寸Wafer/Panel封装颗数

图三 翘曲量定义

图四 不同Warpage类型

图五 Chip First、Chip Last制程步骤

图六 FujiFilm各固化温度PSPI主要规格

图七 Balance Film构造

图八 Balance Film在Chip Last制程应用步骤

图九 2022~2030年台积电在地化采购比例与目标

表一 各厂商PLP布局

表二 各厂商低温固化PSPI布局